部品を基板に取り込む「基板内蔵部品」

電子情報技術産業協会(JEITA)が3年ぶりに実装技術ロードマップを更新し、「2022年度版 実装技術ロードマップ」(書籍)を2022年7月に発行した。本コラムではロードマップの策定を担当したJEITA Jisso技術ロードマップ専門委員会の協力を得て、ロードマップの概要を本コラムの第377回からシリーズで紹介している。

第448回からは、第4章「電子部品」の概要説明を始めた。この章は「4.1 SMD部品」と「4.2 基板内蔵部品」「4.3 コネクタ」の3つの節で構成される。前回までは「4.1 SMD部品」の概要をご報告してきた。今回からは「4.2 基板内蔵部品」の概要をご説明していく。

「4.2 基板内蔵部品」は、以下の2つの項目によって構成される。「4.2.1 薄膜キャパシタ」と「4.2.2 シリコンキャパシタ」であり、いずれもコンデンサを基板に内蔵させる。コンデンサは、プリント基板やパッケージ基板などに数多く搭載されることが少なくない。このため、基板内蔵のニーズが強い。

大規模高性能プロセッサのパッケージ基板に薄膜キャパシタを内蔵

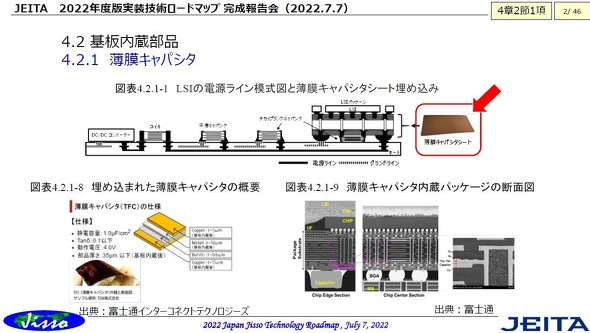

「薄膜キャパシタ(TFCP:Thin Film Capacitor)」とは、プリント基板あるいはパッケージ基板に内蔵させることを目的とした、シート状のキャパシタである。厚みは50μm以下とかなり薄い。基本的な構造は「金属電極膜/高誘電体膜/金属電極膜(MIM:Metal Insulator Metal)」である。金属電極膜の形状を変更することで、目的とする静電容量を得るとともに、信号配線との干渉を避けられる。

薄膜キャパシタの最有力用途は、大規模高性能プロセッサのパッケージ基板だ。従来、数多くのチップ型積層セラミックコンデンサ(MLCC)をパッケージ基板の表面やパッケージ基板の周囲に搭載してきた。電源ライン(電源電圧と接地電圧)の安定化(電源インピーダンスの極小化)が目的である。しかし搭載するMLCCの数は100個を超えるようになっており、実装レイアウトを難しくするとともに、実装面積の増加につながっている。薄膜キャパシタであれば、見かけ上はパッケージ基板と実装面積が変わらない。

「4.2.1 薄膜キャパシタ」の概要を示す図面。上はLSIの電源ライン(電源配線と接地配線)を模式した構造図と薄膜キャパシタの埋め込み位置。左端のDC-DCコンバータから生じた電源供給ラインは、コイル、平滑キャパシタ、デカップリングキャパシタを通じてLSIパッケージへと至る。LSIパッケージ基板に薄膜キャパシタを埋め込むことで、LSI用電源を安定化する。下左は薄膜キャパシタの主な仕様(詳しくは本文テキストに記述)。下右は薄膜キャパシタを内蔵した高速LSIパッケージ基板の断面観察図。多層パッケージ基板の数カ所(電源層と接地層の間)に薄膜キャパシタを埋め込んでいる[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

「4.2.1 薄膜キャパシタ」の概要を示す図面。上はLSIの電源ライン(電源配線と接地配線)を模式した構造図と薄膜キャパシタの埋め込み位置。左端のDC-DCコンバータから生じた電源供給ラインは、コイル、平滑キャパシタ、デカップリングキャパシタを通じてLSIパッケージへと至る。LSIパッケージ基板に薄膜キャパシタを埋め込むことで、LSI用電源を安定化する。下左は薄膜キャパシタの主な仕様(詳しくは本文テキストに記述)。下右は薄膜キャパシタを内蔵した高速LSIパッケージ基板の断面観察図。多層パッケージ基板の数カ所(電源層と接地層の間)に薄膜キャパシタを埋め込んでいる[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)薄膜キャパシタの仕様は例えば静電容量(単位面積当たり)が1μF/cm2、誘電正接(tanδ)が0.1以下、動作電圧が4V、基板内蔵後の厚みが35μmというものだ。高誘電材料はチタン酸バリウム(BaTiO3)、電極材料は一方が銅(Cu)、もう一方がニッケル(Ni)と銅(Cu)となっている。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

からの記事と詳細 ( 電子部品を基板に内蔵させて実装面積を減らす - EE Times Japan )

https://ift.tt/y3KqmDL

No comments:

Post a Comment